ZYNQ_AXI总线

[TOC]

AXI(Advanced extensible Interface)总线是连通PS(programmable system)和PL(programmable logic)的一个总线协议,最终的形式就相当于PL块作为一个ip core 挂载在AXI总线上,然后由PS调用

##Accelerator Coherency Port, AXI_ACP (加速一致性接口)

CSDN_ACP

多核架构下定义的一种接口,用于管理DMA(direct memory access)之类不带缓存的AXI外设

PS端是Slave接口,一通道

##High Performance,AXI_HP

CNBLOG_AXI

高性能/带宽的AXI3.0标准接口,

PL模块作为主设备连接。主要用于PL访问PS上的存储器(DDR和On-Chip RAM)

4通道,作为从机端

##General Port,AXI_GP

AXI_XILINX

通用AXI接口,总共4个,两主两从

可以布一般的外设(低速)

###axi_interconnect

IP_CORE_DATA_SHEET

GREAT_TECH

互联矩阵,相当于时分复用M个axi通道来挂载更多的外设

握手协议就是一个三态输出门(可以回想数电书,哈哈哈哈哈哈哈哈)

##通道协议

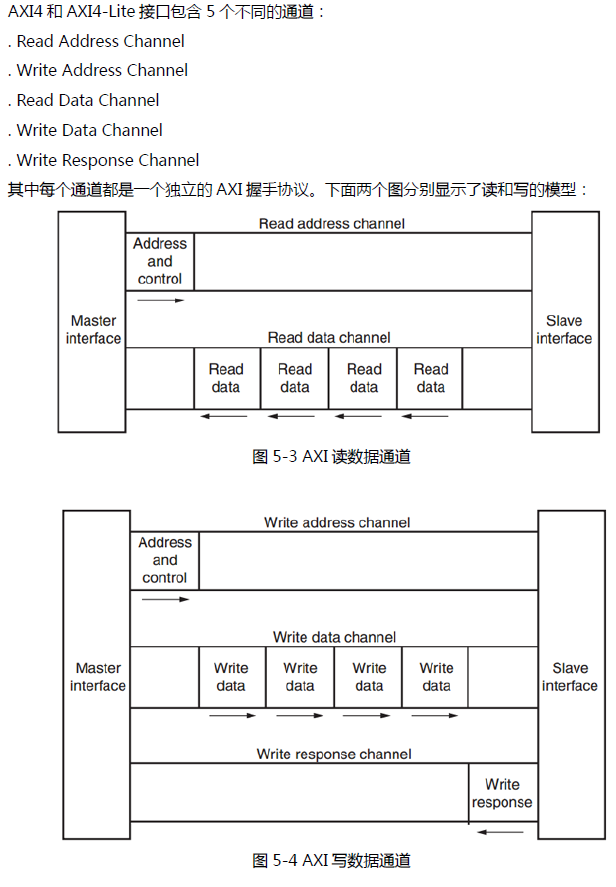

以下图片来源于黑金zynq教学

##summary

- 用于赶项目进度,看了的资料就不整理成blog了,但是会保存在blog里面,后面跑通了再回头补全吧,其它博客或者官方说明文件都写得很好,我的博客只有寥寥几个字感性认识一下而已,没啥价值,还是读别人的东西比较好(毕竟赶时间嘛)

- 所以zynq中总共9个物理接口GP接口是32位的低性能接口,理论带宽600MB/s,而HP和ACP接口为64位高性能接口,理论带宽1200MB/s。有人会问,为什么高性能接口不做成主机接口呢?这样可以由ARM发起高速数据传输。答案是高性能接口根本不需要ARM CPU发起负责数据搬移,真正的搬运工是位于PL中的DMA控制器。